Bring in sdk as its broken

Far, Far to much crap to fix with regex now

This commit is contained in:

Submodule source/Core/BSP/Magic/bl_mcu_sdk deleted from 8742503a9e

171

source/Core/BSP/Magic/bl_mcu_sdk/.clang-format

Normal file

171

source/Core/BSP/Magic/bl_mcu_sdk/.clang-format

Normal file

@@ -0,0 +1,171 @@

|

||||

# clang-format configuration file. Intended for clang-format >= 11.0

|

||||

#

|

||||

# For more information, see:

|

||||

#

|

||||

# https://clang.llvm.org/docs/ClangFormat.html

|

||||

# https://clang.llvm.org/docs/ClangFormatStyleOptions.html

|

||||

#

|

||||

---

|

||||

# 语言: None, Cpp, Java, JavaScript, ObjC, Proto, TableGen, TextProto

|

||||

Language: Cpp

|

||||

# BasedOnStyle: LLVM

|

||||

# 访问说明符(public、private等)的偏移

|

||||

AccessModifierOffset: -4

|

||||

# 开括号(开圆括号、开尖括号、开方括号)后的对齐: Align, DontAlign, AlwaysBreak(总是在开括号后换行)

|

||||

AlignAfterOpenBracket: Align

|

||||

# 连续赋值时,对齐所有等号

|

||||

AlignConsecutiveAssignments: false

|

||||

# 对齐位域

|

||||

AlignConsecutiveBitFields: true

|

||||

# 连续声明时,对齐所有声明的变量名

|

||||

AlignConsecutiveDeclarations: false

|

||||

# 连续宏时,进行对齐

|

||||

AlignConsecutiveMacros: true

|

||||

# 左对齐逃脱换行(使用反斜杠换行)的反斜杠

|

||||

AlignEscapedNewlines: Left

|

||||

# 水平对齐二元和三元表达式的操作数

|

||||

AlignOperands: true

|

||||

# 对齐连续的尾随的注释

|

||||

AlignTrailingComments: true

|

||||

# 允许函数声明的所有参数在放在下一行

|

||||

AllowAllParametersOfDeclarationOnNextLine: false

|

||||

# 允许短的块放在同一行

|

||||

AllowShortBlocksOnASingleLine: false

|

||||

# 允许短的case标签放在同一行

|

||||

AllowShortCaseLabelsOnASingleLine: false

|

||||

# 允许短的函数放在同一行: None, InlineOnly(定义在类中), Empty(空函数), Inline(定义在类中,空函数), All

|

||||

AllowShortFunctionsOnASingleLine: None

|

||||

# 允许短的if语句保持在同一行

|

||||

AllowShortIfStatementsOnASingleLine: false

|

||||

# 允许短的循环保持在同一行

|

||||

AllowShortLoopsOnASingleLine: false

|

||||

# 总是在定义返回类型后换行(deprecated)

|

||||

AlwaysBreakAfterDefinitionReturnType: None

|

||||

# 总是在返回类型后换行: None, All, TopLevel(顶级函数,不包括在类中的函数),

|

||||

# AllDefinitions(所有的定义,不包括声明), TopLevelDefinitions(所有的顶级函数的定义)

|

||||

AlwaysBreakAfterReturnType: None

|

||||

# 总是在多行string字面量前换行

|

||||

AlwaysBreakBeforeMultilineStrings: false

|

||||

# 总是在template声明后换行

|

||||

AlwaysBreakTemplateDeclarations: false

|

||||

# false表示函数实参要么都在同一行,要么都各自一行

|

||||

BinPackArguments: true

|

||||

# false表示所有形参要么都在同一行,要么都各自一行

|

||||

BinPackParameters: true

|

||||

# 大括号换行,只有当BreakBeforeBraces设置为Custom时才有效

|

||||

BraceWrapping:

|

||||

AfterClass: false

|

||||

AfterControlStatement: false

|

||||

AfterEnum: false

|

||||

AfterFunction: true

|

||||

AfterNamespace: false

|

||||

AfterObjCDeclaration: false

|

||||

AfterStruct: false

|

||||

AfterUnion: false

|

||||

AfterExternBlock: false # Unknown to clang-format-5.0

|

||||

BeforeCatch: false

|

||||

BeforeElse: false

|

||||

IndentBraces: false

|

||||

SplitEmptyFunction: true # Unknown to clang-format-4.0

|

||||

SplitEmptyRecord: true # Unknown to clang-format-4.0

|

||||

SplitEmptyNamespace: true # Unknown to clang-format-4.0

|

||||

# 在二元运算符前换行: None(在操作符后换行), NonAssignment(在非赋值的操作符前换行), All(在操作符前换行)

|

||||

BreakBeforeBinaryOperators: None

|

||||

BreakBeforeBraces: Custom

|

||||

#BreakBeforeInheritanceComma: false # Unknown to clang-format-4.0

|

||||

# 在三元运算符前换行

|

||||

BreakBeforeTernaryOperators: false

|

||||

# 在构造函数的初始化列表的逗号前换行

|

||||

BreakConstructorInitializersBeforeComma: false

|

||||

BreakAfterJavaFieldAnnotations: false

|

||||

BreakStringLiterals: false

|

||||

# 每行字符的限制,0表示没有限制

|

||||

ColumnLimit: 0

|

||||

# 描述具有特殊意义的注释的正则表达式,它不应该被分割为多行或以其它方式改变

|

||||

CommentPragmas: '^ IWYU pragma:'

|

||||

CompactNamespaces: false # Unknown to clang-format-4.0

|

||||

# 构造函数的初始化列表要么都在同一行,要么都各自一行

|

||||

ConstructorInitializerAllOnOneLineOrOnePerLine: false

|

||||

# 构造函数的初始化列表的缩进宽度

|

||||

ConstructorInitializerIndentWidth: 4

|

||||

# 延续的行的缩进宽度

|

||||

ContinuationIndentWidth: 4

|

||||

# 去除C++11的列表初始化的大括号{后和}前的空格

|

||||

Cpp11BracedListStyle: false

|

||||

# 继承最常用的指针和引用的对齐方式

|

||||

DerivePointerAlignment: false

|

||||

# 关闭格式化

|

||||

DisableFormat: false

|

||||

ForEachMacros:

|

||||

- 'SHELL_EXPORT_CMD'

|

||||

|

||||

# 自动检测函数的调用和定义是否被格式为每行一个参数(Experimental)

|

||||

ExperimentalAutoDetectBinPacking: false

|

||||

# 缩进case标签

|

||||

IndentCaseLabels: true

|

||||

# 缩进宽度

|

||||

IndentWidth: 4

|

||||

# 函数返回类型换行时,缩进函数声明或函数定义的函数名

|

||||

IndentWrappedFunctionNames: false

|

||||

# 保留在块开始处的空行

|

||||

KeepEmptyLinesAtTheStartOfBlocks: false

|

||||

# 开始一个块的宏的正则表达式

|

||||

MacroBlockBegin: ''

|

||||

# 结束一个块的宏的正则表达式

|

||||

MacroBlockEnd: ''

|

||||

# 连续空行的最大数量

|

||||

MaxEmptyLinesToKeep: 1

|

||||

# 命名空间的缩进: None, Inner(缩进嵌套的命名空间中的内容), All

|

||||

NamespaceIndentation: None

|

||||

# 使用ObjC块时缩进宽度

|

||||

ObjCBlockIndentWidth: 4

|

||||

# 在ObjC的@property后添加一个空格

|

||||

ObjCSpaceAfterProperty: false

|

||||

# 在ObjC的protocol列表前添加一个空格

|

||||

ObjCSpaceBeforeProtocolList: true

|

||||

# 在call(后对函数调用换行的penalty

|

||||

PenaltyBreakBeforeFirstCallParameter: 30

|

||||

# 在一个注释中引入换行的penalty

|

||||

PenaltyBreakComment: 10

|

||||

# 第一次在<<前换行的penalty

|

||||

PenaltyBreakFirstLessLess: 0

|

||||

# 在一个字符串字面量中引入换行的penalty

|

||||

PenaltyBreakString: 10

|

||||

# 对于每个在行字符数限制之外的字符的penalty

|

||||

PenaltyExcessCharacter: 100

|

||||

# 将函数的返回类型放到它自己的行的penalty

|

||||

PenaltyReturnTypeOnItsOwnLine: 60

|

||||

# 指针和引用的对齐: Left, Right, Middle

|

||||

PointerAlignment: Right

|

||||

# 允许重新排版注释

|

||||

ReflowComments: false

|

||||

# 允许排序#include

|

||||

SortIncludes: false

|

||||

# 在C风格类型转换后添加空格

|

||||

SpaceAfterCStyleCast: false

|

||||

# 在赋值运算符之前添加空格

|

||||

SpaceBeforeAssignmentOperators: true

|

||||

# 开圆括号之前添加一个空格: Never, ControlStatements, Always

|

||||

SpaceBeforeParens: ControlStatements

|

||||

# 在空的圆括号中添加空格

|

||||

SpaceInEmptyParentheses: false

|

||||

# 在尾随的评论前添加的空格数(只适用于//)

|

||||

SpacesBeforeTrailingComments: 1

|

||||

# 在尖括号的<后和>前添加空格

|

||||

SpacesInAngles: false

|

||||

# 在容器(ObjC和JavaScript的数组和字典等)字面量中添加空格

|

||||

SpacesInContainerLiterals: false

|

||||

# 在C风格类型转换的括号中添加空格

|

||||

SpacesInCStyleCastParentheses: false

|

||||

# 在圆括号的(后和)前添加空格

|

||||

SpacesInParentheses: false

|

||||

# 在方括号的[后和]前添加空格,lamda表达式和未指明大小的数组的声明不受影响

|

||||

SpacesInSquareBrackets: false

|

||||

# 标准: Cpp03, Cpp11, Auto

|

||||

Standard: Cpp03

|

||||

# tab宽度

|

||||

TabWidth: 4

|

||||

# 使用tab字符: Never, ForIndentation, ForContinuationAndIndentation, Always

|

||||

UseTab: Never

|

||||

...

|

||||

|

||||

179

source/Core/BSP/Magic/bl_mcu_sdk/.cproject

Normal file

179

source/Core/BSP/Magic/bl_mcu_sdk/.cproject

Normal file

@@ -0,0 +1,179 @@

|

||||

<?xml version="1.0" encoding="UTF-8" standalone="no"?>

|

||||

<?fileVersion 4.0.0?><cproject storage_type_id="org.eclipse.cdt.core.XmlProjectDescriptionStorage">

|

||||

<storageModule moduleId="org.eclipse.cdt.core.settings">

|

||||

<cconfiguration id="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072">

|

||||

<storageModule buildSystemId="org.eclipse.cdt.managedbuilder.core.configurationDataProvider" id="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072" moduleId="org.eclipse.cdt.core.settings" name="Default">

|

||||

<externalSettings/>

|

||||

<extensions>

|

||||

<extension id="org.eclipse.cdt.core.ELF" point="org.eclipse.cdt.core.BinaryParser"/>

|

||||

<extension id="org.eclipse.cdt.core.GASErrorParser" point="org.eclipse.cdt.core.ErrorParser"/>

|

||||

<extension id="org.eclipse.cdt.core.GmakeErrorParser" point="org.eclipse.cdt.core.ErrorParser"/>

|

||||

<extension id="org.eclipse.cdt.core.GLDErrorParser" point="org.eclipse.cdt.core.ErrorParser"/>

|

||||

<extension id="org.eclipse.cdt.core.CWDLocator" point="org.eclipse.cdt.core.ErrorParser"/>

|

||||

<extension id="org.eclipse.cdt.core.GCCErrorParser" point="org.eclipse.cdt.core.ErrorParser"/>

|

||||

</extensions>

|

||||

</storageModule>

|

||||

<storageModule moduleId="cdtBuildSystem" version="4.0.0">

|

||||

<configuration artifactName="${ProjName}" buildProperties="" description="" id="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072" name="Default" optionalBuildProperties="org.eclipse.cdt.docker.launcher.containerbuild.property.volumes=,org.eclipse.cdt.docker.launcher.containerbuild.property.selectedvolumes=" parent="org.eclipse.cdt.build.core.emptycfg">

|

||||

<folderInfo id="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072.1792346702" name="/" resourcePath="">

|

||||

<toolChain id="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.497065614" name="RISC-V Cross GCC" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.prefix.1352229726" name="Prefix" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.prefix" value="riscv64-unknown-elf-" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.suffix.1688033986" name="Suffix" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.suffix"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.c.1872432415" name="C compiler" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.c" value="gcc" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.cpp.2078105401" name="C++ compiler" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.cpp" value="g++" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.ar.1831101806" name="Archiver" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.ar" value="ar" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.objcopy.1448757246" name="Hex/Bin converter" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.objcopy" value="objcopy" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.objdump.1075129316" name="Listing generator" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.objdump" value="objdump" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.size.1742672886" name="Size command" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.size" value="size" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.make.1314958796" name="Build command" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.make" value="make" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.rm.1915887520" name="Remove command" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.command.rm" value="rm" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.useglobalpath.1924003386" name="Use global path" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.useglobalpath"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.path.704067905" name="Path" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.path"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.createflash.627202708" name="Create flash image" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.createflash" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.createlisting.1219461309" name="Create extended listing" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.createlisting"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.printsize.907545928" name="Print size" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.addtools.printsize" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.base.1015262120" name="Architecture" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.base"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.multiply.1306384982" name="Multiply extension (RVM)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.multiply"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.atomic.1489908576" name="Atomic extension (RVA)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.atomic"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.fp.165133640" name="Floating point" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.fp"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.compressed.1875289751" name="Compressed extension (RVC)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.isa.compressed"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.abi.integer.492284435" name="Integer ABI" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.abi.integer"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.abi.fp.1841793115" name="Floating point ABI" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.abi.fp"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.tune.1108911638" name="Tuning" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.tune"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.codemodel.1594234601" name="Code model" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.codemodel"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.smalldatalimit.1532183408" name="Small data limit" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.smalldatalimit"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.align.1487992932" name="Align" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.align"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.saverestore.641693495" name="Small prologue/epilogue (-msave-restore)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.saverestore"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.memcpy.1612253810" name="Force string operations to call library functions (-mmemcpy)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.memcpy"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.plt.327409451" name="Allow use of PLTs (-mplt)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.plt"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.fdiv.471747874" name="Floating-point divide/sqrt instructions (-mfdiv)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.fdiv"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.div.1454578867" name="Integer divide instructions (-mdiv)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.div"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.other.2061222983" name="Other target flags" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.target.other"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.level.444746854" name="Optimization Level" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.level"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.messagelength.1137303046" name="Message length (-fmessage-length=0)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.messagelength"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.signedchar.1261641000" name="'char' is signed (-fsigned-char)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.signedchar"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.functionsections.1037457578" name="Function sections (-ffunction-sections)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.functionsections"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.datasections.505001509" name="Data sections (-fdata-sections)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.datasections"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nocommon.993751625" name="No common unitialized (-fno-common)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nocommon"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.noinlinefunctions.756959633" name="Do not inline functions (-fno-inline-functions)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.noinlinefunctions"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.freestanding.1590959906" name="Assume freestanding environment (-ffreestanding)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.freestanding"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nobuiltin.1042039327" name="Disable builtin (-fno-builtin)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nobuiltin"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.spconstant.1039548956" name="Single precision constants (-fsingle-precision-constant)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.spconstant"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.PIC.1985811521" name="Position independent code (-fPIC)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.PIC"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.lto.1051530800" name="Link-time optimizer (-flto)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.lto"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nomoveloopinvariants.1205914795" name="Disable loop invariant move (-fno-move-loop-invariants)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.nomoveloopinvariants"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.other.1954151846" name="Other optimization flags" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.optimization.other"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.name.1744383700" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.name" value="RISC-V GCC/Newlib" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.id.493085227" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.toolchain.id" value="2262347901" valueType="string"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.syntaxonly.258175649" name="Check syntax only (-fsyntax-only)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.syntaxonly"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pedantic.1226214321" name="Pedantic (-pedantic)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pedantic"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pedanticerrors.110062487" name="Pedantic warnings as errors (-pedantic-errors)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pedanticerrors"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.nowarn.1919671717" name="Inhibit all warnings (-w)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.nowarn"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.unused.1821427624" name="Warn on various unused elements (-Wunused)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.unused"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.uninitialized.292398014" name="Warn on uninitialized variables (-Wuninitialised)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.uninitialized"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.allwarn.1309277289" name="Enable all common warnings (-Wall)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.allwarn"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.extrawarn.1558226400" name="Enable extra warnings (-Wextra)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.extrawarn"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.missingdeclaration.586697590" name="Warn on undeclared global function (-Wmissing-declaration)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.missingdeclaration"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.conversion.954958860" name="Warn on implicit conversions (-Wconversion)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.conversion"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pointerarith.563944459" name="Warn if pointer arithmetic (-Wpointer-arith)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.pointerarith"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.padded.1545777759" name="Warn if padding is included (-Wpadded)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.padded"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.shadow.1629270130" name="Warn if shadowed variable (-Wshadow)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.shadow"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.logicalop.658467865" name="Warn if suspicious logical ops (-Wlogical-op)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.logicalop"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.agreggatereturn.971552745" name="Warn if struct is returned (-Wagreggate-return)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.agreggatereturn"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.floatequal.1598374590" name="Warn if floats are compared as equal (-Wfloat-equal)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.floatequal"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.toerrors.1396465302" name="Generate errors instead of warnings (-Werror)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.toerrors"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.other.1062181782" name="Other warning flags" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.warnings.other"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.level.1738140850" name="Debug level" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.level"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.format.792481645" name="Debug format" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.format"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.prof.953900793" name="Generate prof information (-p)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.prof"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.gprof.202548387" name="Generate gprof information (-pg)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.gprof"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.other.1881550968" name="Other debugging flags" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.debugging.other"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.showDevicesTab.975549113" name="showDevicesTab" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.showDevicesTab"/>

|

||||

<targetPlatform archList="all" binaryParser="org.eclipse.cdt.core.ELF" id="ilg.gnumcueclipse.managedbuild.cross.riscv.targetPlatform.1497718471" isAbstract="false" osList="all" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.targetPlatform"/>

|

||||

<builder autoBuildTarget="all" cleanBuildTarget="clean" command="make" enableAutoBuild="false" enableCleanBuild="true" enabledIncrementalBuild="true" id="ilg.gnumcueclipse.managedbuild.cross.riscv.builder.1100306583" incrementalBuildTarget="BOARD=BL702_EVB APP=hellowd SAPP=helloworld" keepEnvironmentInBuildfile="false" managedBuildOn="false" name="Gnu Make Builder" parallelBuildOn="false" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.builder"/>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.assembler.1060786402" name="GNU RISC-V Cross Assembler" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.assembler">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.assembler.usepreprocessor.154864423" name="Use preprocessor" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.assembler.usepreprocessor" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<inputType id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.assembler.input.1096558861" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.assembler.input"/>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler.952554633" name="GNU RISC-V Cross C Compiler" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler">

|

||||

<inputType id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler.input.141010239" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler.input"/>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler.1200181396" name="GNU RISC-V Cross C++ Compiler" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler">

|

||||

<inputType id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler.input.1522176966" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler.input"/>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.linker.734083223" name="GNU RISC-V Cross C Linker" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.linker">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.c.linker.gcsections.528465909" name="Remove unused sections (-Xlinker --gc-sections)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.c.linker.gcsections" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.linker.2027828701" name="GNU RISC-V Cross C++ Linker" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.linker">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.cpp.linker.gcsections.1009157025" name="Remove unused sections (-Xlinker --gc-sections)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.cpp.linker.gcsections" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<inputType id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.linker.input.807068426" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.linker.input">

|

||||

<additionalInput kind="additionalinputdependency" paths="$(USER_OBJS)"/>

|

||||

<additionalInput kind="additionalinput" paths="$(LIBS)"/>

|

||||

</inputType>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.archiver.1266046767" name="GNU RISC-V Cross Archiver" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.archiver"/>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.createflash.1181214240" name="GNU RISC-V Cross Create Flash Image" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.createflash"/>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.createlisting.1777652181" name="GNU RISC-V Cross Create Listing" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.createlisting">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.source.1728454125" name="Display source (--source|-S)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.source" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.allheaders.503927789" name="Display all headers (--all-headers|-x)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.allheaders" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.demangle.603185590" name="Demangle names (--demangle|-C)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.demangle" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.linenumbers.1295754826" name="Display line numbers (--line-numbers|-l)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.linenumbers" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.wide.312765386" name="Wide lines (--wide|-w)" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.createlisting.wide" useByScannerDiscovery="false" value="true" valueType="boolean"/>

|

||||

</tool>

|

||||

<tool id="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.printsize.964975723" name="GNU RISC-V Cross Print Size" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.tool.printsize">

|

||||

<option id="ilg.gnumcueclipse.managedbuild.cross.riscv.option.printsize.format.795673591" name="Size format" superClass="ilg.gnumcueclipse.managedbuild.cross.riscv.option.printsize.format" useByScannerDiscovery="false"/>

|

||||

</tool>

|

||||

</toolChain>

|

||||

</folderInfo>

|

||||

</configuration>

|

||||

</storageModule>

|

||||

<storageModule moduleId="org.eclipse.cdt.core.externalSettings"/>

|

||||

<storageModule moduleId="ilg.gnumcueclipse.managedbuild.packs"/>

|

||||

</cconfiguration>

|

||||

</storageModule>

|

||||

<storageModule moduleId="cdtBuildSystem" version="4.0.0">

|

||||

<project id="bl_mcu_sdk.null.805808530" name="bl_mcu_sdk"/>

|

||||

</storageModule>

|

||||

<storageModule moduleId="scannerConfiguration">

|

||||

<autodiscovery enabled="true" problemReportingEnabled="true" selectedProfileId=""/>

|

||||

<scannerConfigBuildInfo instanceId="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072;ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072.1792346702;ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler.1200181396;ilg.gnumcueclipse.managedbuild.cross.riscv.tool.cpp.compiler.input.1522176966">

|

||||

<autodiscovery enabled="true" problemReportingEnabled="true" selectedProfileId=""/>

|

||||

</scannerConfigBuildInfo>

|

||||

<scannerConfigBuildInfo instanceId="ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072;ilg.gnumcueclipse.managedbuild.cross.riscv.toolchain.base.528944072.1792346702;ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler.952554633;ilg.gnumcueclipse.managedbuild.cross.riscv.tool.c.compiler.input.141010239">

|

||||

<autodiscovery enabled="true" problemReportingEnabled="true" selectedProfileId=""/>

|

||||

</scannerConfigBuildInfo>

|

||||

</storageModule>

|

||||

<storageModule moduleId="org.eclipse.cdt.core.LanguageSettingsProviders"/>

|

||||

<storageModule moduleId="refreshScope" versionNumber="2">

|

||||

<configuration configurationName="Default">

|

||||

<resource resourceType="PROJECT" workspacePath="/bl_mcu_sdk"/>

|

||||

</configuration>

|

||||

</storageModule>

|

||||

<storageModule moduleId="org.eclipse.cdt.make.core.buildtargets">

|

||||

<buildTargets>

|

||||

<target name="bl_make" path="" targetID="org.eclipse.cdt.build.MakeTargetBuilder">

|

||||

<buildCommand>make</buildCommand>

|

||||

<buildArguments>build BOARD=bl706_iot</buildArguments>

|

||||

<buildTarget>APP=helloworld</buildTarget>

|

||||

<stopOnError>true</stopOnError>

|

||||

<useDefaultCommand>false</useDefaultCommand>

|

||||

<runAllBuilders>true</runAllBuilders>

|

||||

</target>

|

||||

<target name="bl_clean" path="" targetID="org.eclipse.cdt.build.MakeTargetBuilder">

|

||||

<buildCommand>make</buildCommand>

|

||||

<buildTarget>clean</buildTarget>

|

||||

<stopOnError>true</stopOnError>

|

||||

<useDefaultCommand>false</useDefaultCommand>

|

||||

<runAllBuilders>true</runAllBuilders>

|

||||

</target>

|

||||

<target name="download" path="" targetID="org.eclipse.cdt.build.MakeTargetBuilder">

|

||||

<buildCommand>make</buildCommand>

|

||||

<buildArguments>INTERFACE=uart COMx=com49</buildArguments>

|

||||

<buildTarget>download</buildTarget>

|

||||

<stopOnError>true</stopOnError>

|

||||

<useDefaultCommand>false</useDefaultCommand>

|

||||

<runAllBuilders>true</runAllBuilders>

|

||||

</target>

|

||||

</buildTargets>

|

||||

</storageModule>

|

||||

</cproject>

|

||||

27

source/Core/BSP/Magic/bl_mcu_sdk/.project

Normal file

27

source/Core/BSP/Magic/bl_mcu_sdk/.project

Normal file

@@ -0,0 +1,27 @@

|

||||

<?xml version="1.0" encoding="UTF-8"?>

|

||||

<projectDescription>

|

||||

<name>bl_mcu_sdk</name>

|

||||

<comment></comment>

|

||||

<projects>

|

||||

</projects>

|

||||

<buildSpec>

|

||||

<buildCommand>

|

||||

<name>org.eclipse.cdt.managedbuilder.core.genmakebuilder</name>

|

||||

<triggers>clean,full,incremental,</triggers>

|

||||

<arguments>

|

||||

</arguments>

|

||||

</buildCommand>

|

||||

<buildCommand>

|

||||

<name>org.eclipse.cdt.managedbuilder.core.ScannerConfigBuilder</name>

|

||||

<triggers>full,incremental,</triggers>

|

||||

<arguments>

|

||||

</arguments>

|

||||

</buildCommand>

|

||||

</buildSpec>

|

||||

<natures>

|

||||

<nature>org.eclipse.cdt.core.cnature</nature>

|

||||

<nature>org.eclipse.cdt.core.ccnature</nature>

|

||||

<nature>org.eclipse.cdt.managedbuilder.core.managedBuildNature</nature>

|

||||

<nature>org.eclipse.cdt.managedbuilder.core.ScannerConfigNature</nature>

|

||||

</natures>

|

||||

</projectDescription>

|

||||

19

source/Core/BSP/Magic/bl_mcu_sdk/CMakeLists.txt

Normal file

19

source/Core/BSP/Magic/bl_mcu_sdk/CMakeLists.txt

Normal file

@@ -0,0 +1,19 @@

|

||||

cmake_minimum_required(VERSION 3.15)

|

||||

set(CMAKE_TOOLCHAIN_FILE ${CMAKE_SOURCE_DIR}/tools/cmake/riscv64-unknown-elf-gcc.cmake)

|

||||

include(${CMAKE_SOURCE_DIR}/drivers/${CHIP}_driver/cpu_flags.cmake)

|

||||

include(${CMAKE_SOURCE_DIR}/tools/cmake/compiler_flags.cmake)

|

||||

include(${CMAKE_SOURCE_DIR}/tools/cmake/tools.cmake)

|

||||

|

||||

PROJECT(${BOARD} C CXX ASM)

|

||||

# set(CMAKE_VERBOSE_MAKEFILE ON)

|

||||

ENABLE_LANGUAGE(ASM)

|

||||

|

||||

include_directories(${CMAKE_SOURCE_DIR}/bsp/bsp_common/platform)

|

||||

|

||||

if(IS_DIRECTORY ${CMAKE_SOURCE_DIR}/bsp/board/${CHIP})

|

||||

include_directories(${CMAKE_SOURCE_DIR}/bsp/board/${CHIP})

|

||||

else()

|

||||

message(FATAL_ERROR "${CMAKE_SOURCE_DIR}/bsp/board/${CHIP} is not exist")

|

||||

endif()

|

||||

|

||||

search_application(${CMAKE_SOURCE_DIR}/${APP_DIR})

|

||||

202

source/Core/BSP/Magic/bl_mcu_sdk/LICENSE

Normal file

202

source/Core/BSP/Magic/bl_mcu_sdk/LICENSE

Normal file

@@ -0,0 +1,202 @@

|

||||

|

||||

Apache License

|

||||

Version 2.0, January 2004

|

||||

http://www.apache.org/licenses/

|

||||

|

||||

TERMS AND CONDITIONS FOR USE, REPRODUCTION, AND DISTRIBUTION

|

||||

|

||||

1. Definitions.

|

||||

|

||||

"License" shall mean the terms and conditions for use, reproduction,

|

||||

and distribution as defined by Sections 1 through 9 of this document.

|

||||

|

||||

"Licensor" shall mean the copyright owner or entity authorized by

|

||||

the copyright owner that is granting the License.

|

||||

|

||||

"Legal Entity" shall mean the union of the acting entity and all

|

||||

other entities that control, are controlled by, or are under common

|

||||

control with that entity. For the purposes of this definition,

|

||||

"control" means (i) the power, direct or indirect, to cause the

|

||||

direction or management of such entity, whether by contract or

|

||||

otherwise, or (ii) ownership of fifty percent (50%) or more of the

|

||||

outstanding shares, or (iii) beneficial ownership of such entity.

|

||||

|

||||

"You" (or "Your") shall mean an individual or Legal Entity

|

||||

exercising permissions granted by this License.

|

||||

|

||||

"Source" form shall mean the preferred form for making modifications,

|

||||

including but not limited to software source code, documentation

|

||||

source, and configuration files.

|

||||

|

||||

"Object" form shall mean any form resulting from mechanical

|

||||

transformation or translation of a Source form, including but

|

||||

not limited to compiled object code, generated documentation,

|

||||

and conversions to other media types.

|

||||

|

||||

"Work" shall mean the work of authorship, whether in Source or

|

||||

Object form, made available under the License, as indicated by a

|

||||

copyright notice that is included in or attached to the work

|

||||

(an example is provided in the Appendix below).

|

||||

|

||||

"Derivative Works" shall mean any work, whether in Source or Object

|

||||

form, that is based on (or derived from) the Work and for which the

|

||||

editorial revisions, annotations, elaborations, or other modifications

|

||||

represent, as a whole, an original work of authorship. For the purposes

|

||||

of this License, Derivative Works shall not include works that remain

|

||||

separable from, or merely link (or bind by name) to the interfaces of,

|

||||

the Work and Derivative Works thereof.

|

||||

|

||||

"Contribution" shall mean any work of authorship, including

|

||||

the original version of the Work and any modifications or additions

|

||||

to that Work or Derivative Works thereof, that is intentionally

|

||||

submitted to Licensor for inclusion in the Work by the copyright owner

|

||||

or by an individual or Legal Entity authorized to submit on behalf of

|

||||

the copyright owner. For the purposes of this definition, "submitted"

|

||||

means any form of electronic, verbal, or written communication sent

|

||||

to the Licensor or its representatives, including but not limited to

|

||||

communication on electronic mailing lists, source code control systems,

|

||||

and issue tracking systems that are managed by, or on behalf of, the

|

||||

Licensor for the purpose of discussing and improving the Work, but

|

||||

excluding communication that is conspicuously marked or otherwise

|

||||

designated in writing by the copyright owner as "Not a Contribution."

|

||||

|

||||

"Contributor" shall mean Licensor and any individual or Legal Entity

|

||||

on behalf of whom a Contribution has been received by Licensor and

|

||||

subsequently incorporated within the Work.

|

||||

|

||||

2. Grant of Copyright License. Subject to the terms and conditions of

|

||||

this License, each Contributor hereby grants to You a perpetual,

|

||||

worldwide, non-exclusive, no-charge, royalty-free, irrevocable

|

||||

copyright license to reproduce, prepare Derivative Works of,

|

||||

publicly display, publicly perform, sublicense, and distribute the

|

||||

Work and such Derivative Works in Source or Object form.

|

||||

|

||||

3. Grant of Patent License. Subject to the terms and conditions of

|

||||

this License, each Contributor hereby grants to You a perpetual,

|

||||

worldwide, non-exclusive, no-charge, royalty-free, irrevocable

|

||||

(except as stated in this section) patent license to make, have made,

|

||||

use, offer to sell, sell, import, and otherwise transfer the Work,

|

||||

where such license applies only to those patent claims licensable

|

||||

by such Contributor that are necessarily infringed by their

|

||||

Contribution(s) alone or by combination of their Contribution(s)

|

||||

with the Work to which such Contribution(s) was submitted. If You

|

||||

institute patent litigation against any entity (including a

|

||||

cross-claim or counterclaim in a lawsuit) alleging that the Work

|

||||

or a Contribution incorporated within the Work constitutes direct

|

||||

or contributory patent infringement, then any patent licenses

|

||||

granted to You under this License for that Work shall terminate

|

||||

as of the date such litigation is filed.

|

||||

|

||||

4. Redistribution. You may reproduce and distribute copies of the

|

||||

Work or Derivative Works thereof in any medium, with or without

|

||||

modifications, and in Source or Object form, provided that You

|

||||

meet the following conditions:

|

||||

|

||||

(a) You must give any other recipients of the Work or

|

||||

Derivative Works a copy of this License; and

|

||||

|

||||

(b) You must cause any modified files to carry prominent notices

|

||||

stating that You changed the files; and

|

||||

|

||||

(c) You must retain, in the Source form of any Derivative Works

|

||||

that You distribute, all copyright, patent, trademark, and

|

||||

attribution notices from the Source form of the Work,

|

||||

excluding those notices that do not pertain to any part of

|

||||

the Derivative Works; and

|

||||

|

||||

(d) If the Work includes a "NOTICE" text file as part of its

|

||||

distribution, then any Derivative Works that You distribute must

|

||||

include a readable copy of the attribution notices contained

|

||||

within such NOTICE file, excluding those notices that do not

|

||||

pertain to any part of the Derivative Works, in at least one

|

||||

of the following places: within a NOTICE text file distributed

|

||||

as part of the Derivative Works; within the Source form or

|

||||

documentation, if provided along with the Derivative Works; or,

|

||||

within a display generated by the Derivative Works, if and

|

||||

wherever such third-party notices normally appear. The contents

|

||||

of the NOTICE file are for informational purposes only and

|

||||

do not modify the License. You may add Your own attribution

|

||||

notices within Derivative Works that You distribute, alongside

|

||||

or as an addendum to the NOTICE text from the Work, provided

|

||||

that such additional attribution notices cannot be construed

|

||||

as modifying the License.

|

||||

|

||||

You may add Your own copyright statement to Your modifications and

|

||||

may provide additional or different license terms and conditions

|

||||

for use, reproduction, or distribution of Your modifications, or

|

||||

for any such Derivative Works as a whole, provided Your use,

|

||||

reproduction, and distribution of the Work otherwise complies with

|

||||

the conditions stated in this License.

|

||||

|

||||

5. Submission of Contributions. Unless You explicitly state otherwise,

|

||||

any Contribution intentionally submitted for inclusion in the Work

|

||||

by You to the Licensor shall be under the terms and conditions of

|

||||

this License, without any additional terms or conditions.

|

||||

Notwithstanding the above, nothing herein shall supersede or modify

|

||||

the terms of any separate license agreement you may have executed

|

||||

with Licensor regarding such Contributions.

|

||||

|

||||

6. Trademarks. This License does not grant permission to use the trade

|

||||

names, trademarks, service marks, or product names of the Licensor,

|

||||

except as required for reasonable and customary use in describing the

|

||||

origin of the Work and reproducing the content of the NOTICE file.

|

||||

|

||||

7. Disclaimer of Warranty. Unless required by applicable law or

|

||||

agreed to in writing, Licensor provides the Work (and each

|

||||

Contributor provides its Contributions) on an "AS IS" BASIS,

|

||||

WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or

|

||||

implied, including, without limitation, any warranties or conditions

|

||||

of TITLE, NON-INFRINGEMENT, MERCHANTABILITY, or FITNESS FOR A

|

||||

PARTICULAR PURPOSE. You are solely responsible for determining the

|

||||

appropriateness of using or redistributing the Work and assume any

|

||||

risks associated with Your exercise of permissions under this License.

|

||||

|

||||

8. Limitation of Liability. In no event and under no legal theory,

|

||||

whether in tort (including negligence), contract, or otherwise,

|

||||

unless required by applicable law (such as deliberate and grossly

|

||||

negligent acts) or agreed to in writing, shall any Contributor be

|

||||

liable to You for damages, including any direct, indirect, special,

|

||||

incidental, or consequential damages of any character arising as a

|

||||

result of this License or out of the use or inability to use the

|

||||

Work (including but not limited to damages for loss of goodwill,

|

||||

work stoppage, computer failure or malfunction, or any and all

|

||||

other commercial damages or losses), even if such Contributor

|

||||

has been advised of the possibility of such damages.

|

||||

|

||||

9. Accepting Warranty or Additional Liability. While redistributing

|

||||

the Work or Derivative Works thereof, You may choose to offer,

|

||||

and charge a fee for, acceptance of support, warranty, indemnity,

|

||||

or other liability obligations and/or rights consistent with this

|

||||

License. However, in accepting such obligations, You may act only

|

||||

on Your own behalf and on Your sole responsibility, not on behalf

|

||||

of any other Contributor, and only if You agree to indemnify,

|

||||

defend, and hold each Contributor harmless for any liability

|

||||

incurred by, or claims asserted against, such Contributor by reason

|

||||

of your accepting any such warranty or additional liability.

|

||||

|

||||

END OF TERMS AND CONDITIONS

|

||||

|

||||

APPENDIX: How to apply the Apache License to your work.

|

||||

|

||||

To apply the Apache License to your work, attach the following

|

||||

boilerplate notice, with the fields enclosed by brackets "[]"

|

||||

replaced with your own identifying information. (Don't include

|

||||

the brackets!) The text should be enclosed in the appropriate

|

||||

comment syntax for the file format. We also recommend that a

|

||||

file or class name and description of purpose be included on the

|

||||

same "printed page" as the copyright notice for easier

|

||||

identification within third-party archives.

|

||||

|

||||

Copyright [2020] [BOUFFALO LAB (NANJING) CO., LTD.]

|

||||

|

||||

Licensed under the Apache License, Version 2.0 (the "License");

|

||||

you may not use this file except in compliance with the License.

|

||||

You may obtain a copy of the License at

|

||||

|

||||

http://www.apache.org/licenses/LICENSE-2.0

|

||||

|

||||

Unless required by applicable law or agreed to in writing, software

|

||||

distributed under the License is distributed on an "AS IS" BASIS,

|

||||

WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

|

||||

See the License for the specific language governing permissions and

|

||||

limitations under the License.

|

||||

72

source/Core/BSP/Magic/bl_mcu_sdk/Makefile

Normal file

72

source/Core/BSP/Magic/bl_mcu_sdk/Makefile

Normal file

@@ -0,0 +1,72 @@

|

||||

#common config

|

||||

BOARD?=bl706_iot

|

||||

CHIP?=bl702

|

||||

APP_DIR?=examples

|

||||

APP?=helloworld

|

||||

CPU_ID?=none

|

||||

|

||||

#bootrom config,users do not need it

|

||||

BOOTROM?=n

|

||||

|

||||

#format config

|

||||

FORMAT_DIR?=.

|

||||

|

||||

# The command to remove a file.

|

||||

RM = cmake -E remove_directory

|

||||

|

||||

#flash tool config

|

||||

INTERFACE?=uart

|

||||

COMx?=

|

||||

BAUDRATE ?=2000000

|

||||

ifeq ($(INTERFACE),uart)

|

||||

FLASH_DOWNLOAD_CONFIG:=--chipname=$(CHIP) --interface=uart --port=$(COMx) --baudrate=$(BAUDRATE)

|

||||

else

|

||||

FLASH_DOWNLOAD_CONFIG:=--chipname=$(CHIP) --interface=$(INTERFACE)

|

||||

endif

|

||||

|

||||

#option config to use

|

||||

SUPPORT_FLOAT?=n

|

||||

SUPPORT_ROMAPI?=y

|

||||

SUPPORT_HALAPI?=y

|

||||

SUPPORT_USB_HS?=n

|

||||

SUPPORT_HW_SEC_ENG_DISABLE?=n

|

||||

SUPPORT_BLECONTROLLER_LIB?=

|

||||

|

||||

#cmake definition config

|

||||

cmake_definition+= -DCHIP=$(CHIP)

|

||||

cmake_definition+= -DCPU_ID=$(CPU_ID)

|

||||

cmake_definition+= -DBOARD=$(BOARD)

|

||||

cmake_definition+= -DAPP_DIR=$(APP_DIR)

|

||||

cmake_definition+= -DAPP=$(APP)

|

||||

cmake_definition+= -DBOOTROM=$(BOOTROM)

|

||||

cmake_definition+= -DCONFIG_ROMAPI=$(SUPPORT_ROMAPI)

|

||||

cmake_definition+= -DCONFIG_HALAPI=$(SUPPORT_HALAPI)

|

||||

cmake_definition+= -DCONFIG_PRINT_FLOAT=$(SUPPORT_FLOAT)

|

||||

cmake_definition+= -DCONFIG_USB_HS=$(SUPPORT_USB_HS)

|

||||

cmake_definition+= -DCONFIG_HW_SEC_ENG_DISABLE=$(SUPPORT_HW_SEC_ENG_DISABLE)

|

||||

cmake_definition+= -DCONFIG_BLECONTROLLER_LIB=$(SUPPORT_BLECONTROLLER_LIB)

|

||||

|

||||

build:Makefile

|

||||

cmake -S . -B build -G "Unix Makefiles" $(cmake_definition)

|

||||

cd build && make -j4

|

||||

|

||||

help:

|

||||

@echo "Welcome to MCU SDK cmake build system,commands are as follows:"

|

||||

@echo ""

|

||||

@echo "make clean - Remove all cmake caches and output files"

|

||||

@echo "make SUPPORT_FLOAT=y - Enable float print"

|

||||

@echo "make SUPPORT_USB_HS=y - Enable usb high speed"

|

||||

@echo "make SUPPORT_BLECONTROLLER_LIB=value - Select blecontroller lib,value can be m0s1、m0s1s、std or empty"

|

||||

|

||||

download:

|

||||

./tools/bflb_flash_tool/bflb_mcu_tool $(FLASH_DOWNLOAD_CONFIG)

|

||||

|

||||

format:

|

||||

find $(FORMAT_DIR)/ -name "*.c" -o -name "*.h" -o -name "*.cc" -o -name "*.cpp"| xargs clang-format -style=file -i

|

||||

|

||||

clean:

|

||||

$(RM) out

|

||||

$(RM) build

|

||||

|

||||

.PHONY:build clean download format help

|

||||

|

||||

245

source/Core/BSP/Magic/bl_mcu_sdk/README.md

Normal file

245

source/Core/BSP/Magic/bl_mcu_sdk/README.md

Normal file

@@ -0,0 +1,245 @@

|

||||

[](LICENSE)

|

||||

[]()

|

||||

|

||||

[中文版](README_zh.md)

|

||||

|

||||

# Introduction

|

||||

|

||||

**bl mcu sdk** is an MCU software development kit provided by the Bouffalo Lab Team for BL602/BL604, BL702/BL704/BL706 and other series of chips in the future.

|

||||

|

||||

## Code Framework

|

||||

|

||||

```

|

||||

|

||||

bl_mcu_sdk

|

||||

├── bsp

|

||||

│ ├── board

|

||||

│ │ ├── bl602

|

||||

│ │ └── bl702

|

||||

│ └── bsp_common

|

||||

├── build

|

||||

├── common

|

||||

│ ├── bl_math

|

||||

│ ├── device

|

||||

│ ├── list

|

||||

│ ├── memheap

|

||||

│ ├── misc

|

||||

│ ├── partition

|

||||

│ ├── pid

|

||||

│ ├── ring_buffer

|

||||

│ ├── soft_crc

|

||||

│ └── timestamp

|

||||

├── components

|

||||

│ ├── ble

|

||||

│ ├── fatfs

|

||||

│ ├── freertos

|

||||

│ ├── lvgl

|

||||

│ ├── lwip

|

||||

│ ├── mbedtls

|

||||

│ ├── nmsis

|

||||

│ ├── romfs

|

||||

│ ├── rt-thread

|

||||

│ ├── shell

|

||||

│ ├── tflite

|

||||

│ ├── tiny_jpeg

|

||||

│ ├── usb_stack

|

||||

│ └── xz

|

||||

├── docs

|

||||

│ ├── chipSpecification

|

||||

│ ├── development_guide

|

||||

│ └── development_guide_en

|

||||

├── drivers

|

||||

│ ├── bl602_driver

|

||||

│ └── bl702_driver

|

||||

├── examples

|

||||

│ ├── acomp

|

||||

│ ├── adc

|

||||

│ ├── audio_cube

|

||||

│ ├── ble

|

||||

│ ├── boot2_iap

|

||||

│ ├── camera

|

||||

│ ├── coremark

|

||||

│ ├── cxx

|

||||

│ ├── dac

|

||||

│ ├── dma

|

||||

│ ├── dsp

|

||||

│ ├── emac

|

||||

│ ├── flash

|

||||

│ ├── freertos

|

||||

│ ├── gpio

|

||||

│ ├── hellowd

|

||||

│ ├── i2c

|

||||

│ ├── i2s

|

||||

│ ├── keyscan

|

||||

│ ├── lvgl

|

||||

│ ├── mbedtls

|

||||

│ ├── memheap

|

||||

│ ├── nn

|

||||

│ ├── pka

|

||||

│ ├── pm

|

||||

│ ├── psram

|

||||

│ ├── pwm

|

||||

│ ├── qdec

|

||||

│ ├── rt-thread

|

||||

│ ├── rtc

|

||||

│ ├── shell

|

||||

│ ├── spi

|

||||

│ ├── systick

|

||||

│ ├── tensorflow

|

||||

│ ├── timer

|

||||

│ ├── uart

|

||||

│ └── usb

|

||||

├── out

|

||||

└── tools

|

||||

├── bflb_flash_tool

|

||||

├── cdk_flashloader

|

||||

├── cmake

|

||||

└── openocd

|

||||

```

|

||||

|

||||

- **bsp/board** : store the board-level description file such as `clock_config.h` (describes the clock configuration file) `pinmux_config.h` (describes the io function file) `peripheral_config.h` (describes the default configuration file of the peripheral) , These files together describe the board hardware information.

|

||||

- **bsp/bsp_common** : store some common peripheral driver codes related to the board.

|

||||

- **common** : store some common functions and macros that chip drivers will need.

|

||||

- **components** : store the third-party library public component library.

|

||||

- **drivers** : store bouffalo series of chip drivers.

|

||||

- **examples** : store the official sample code.

|

||||

- **tools** : store toolkits related to compiling and downloading.

|

||||

- **docs** : store tutorial documents and other help information.

|

||||

- **build** : store cmake cache files.

|

||||

- **out** : store the bin and map file generated after compiling and linking.

|

||||

|

||||

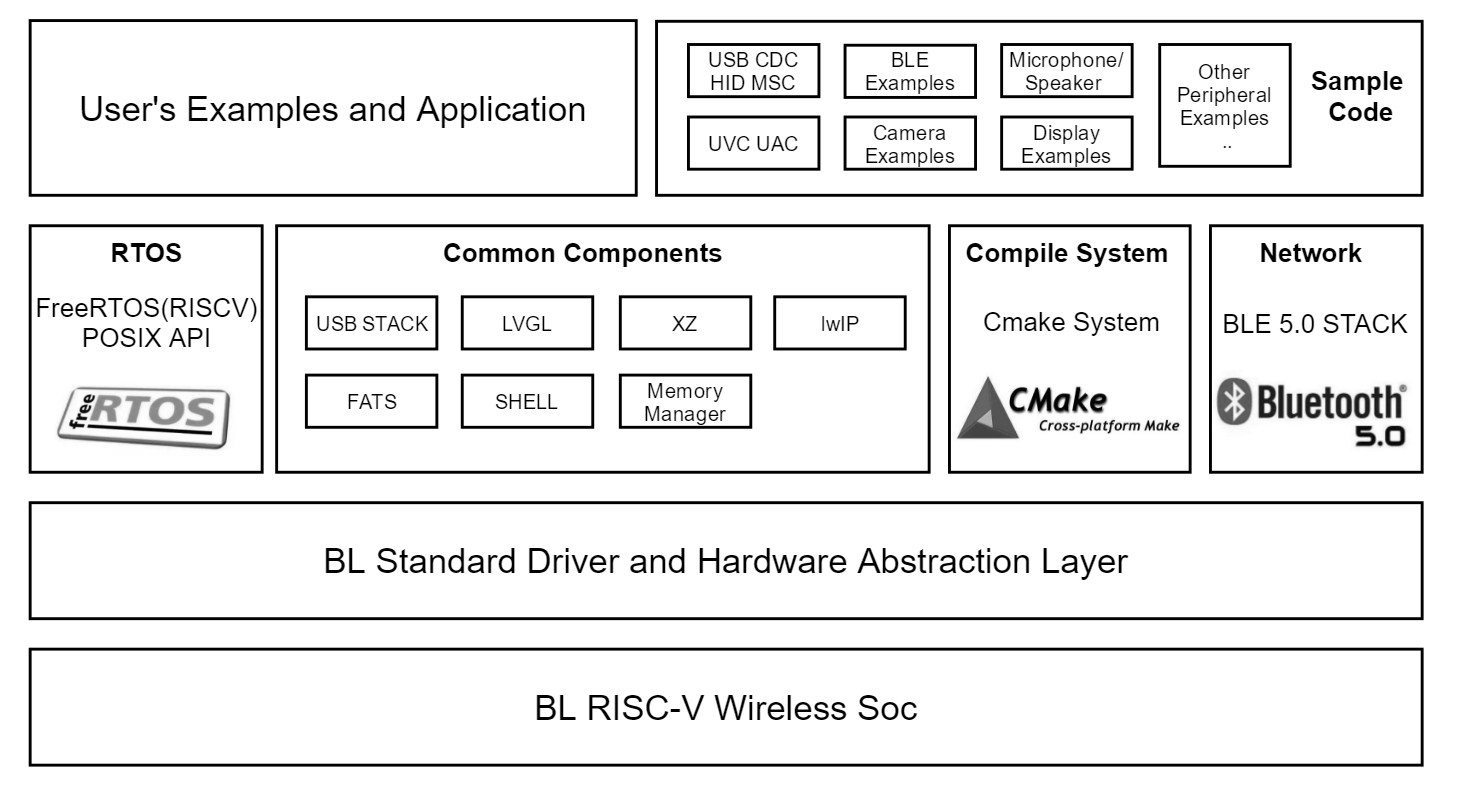

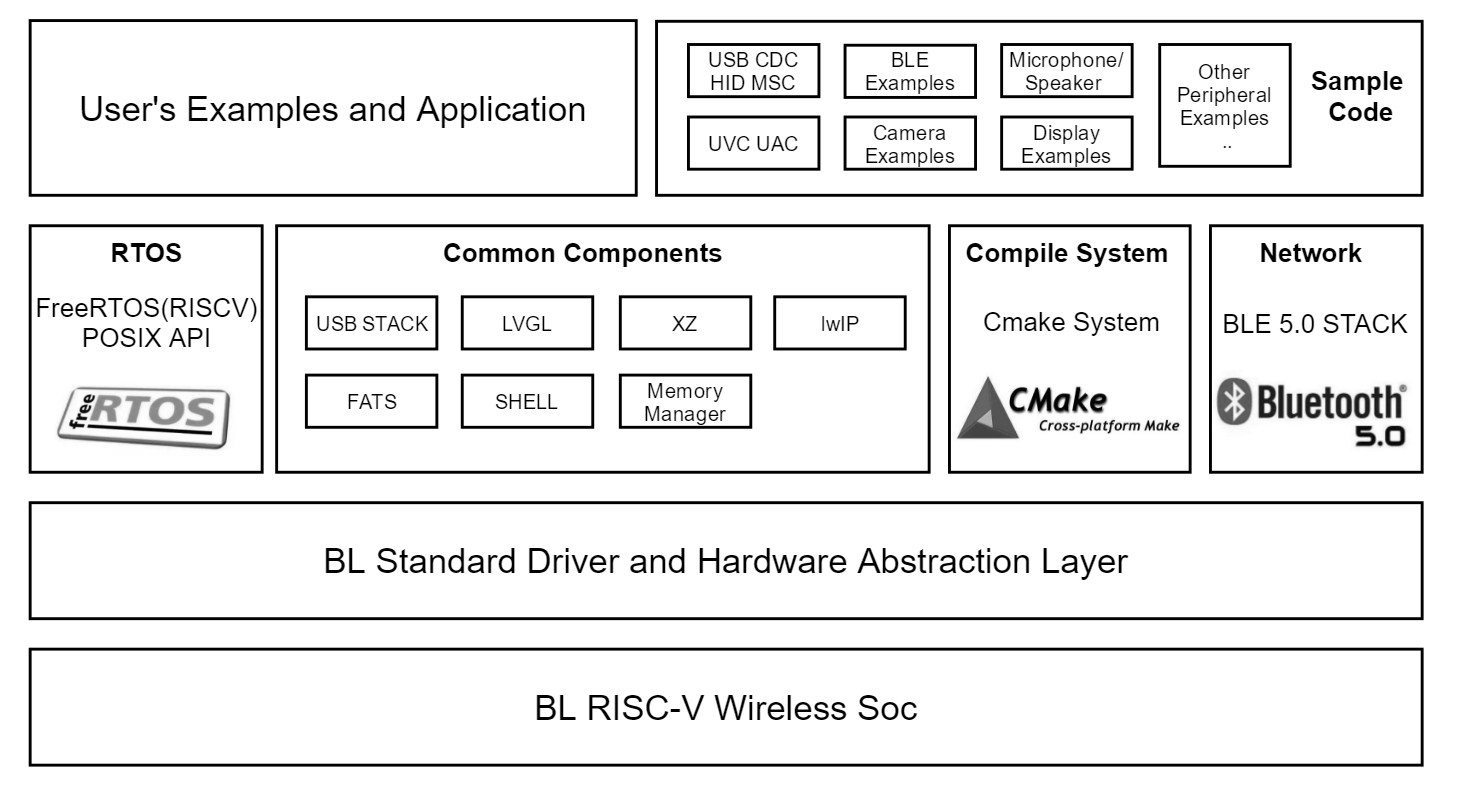

## Hierarchy

|

||||

|

||||

[](https://imgtu.com/i/RpUVoj)

|

||||

|

||||

# Resources

|

||||

|

||||

## Hardware Resources

|

||||

|

||||

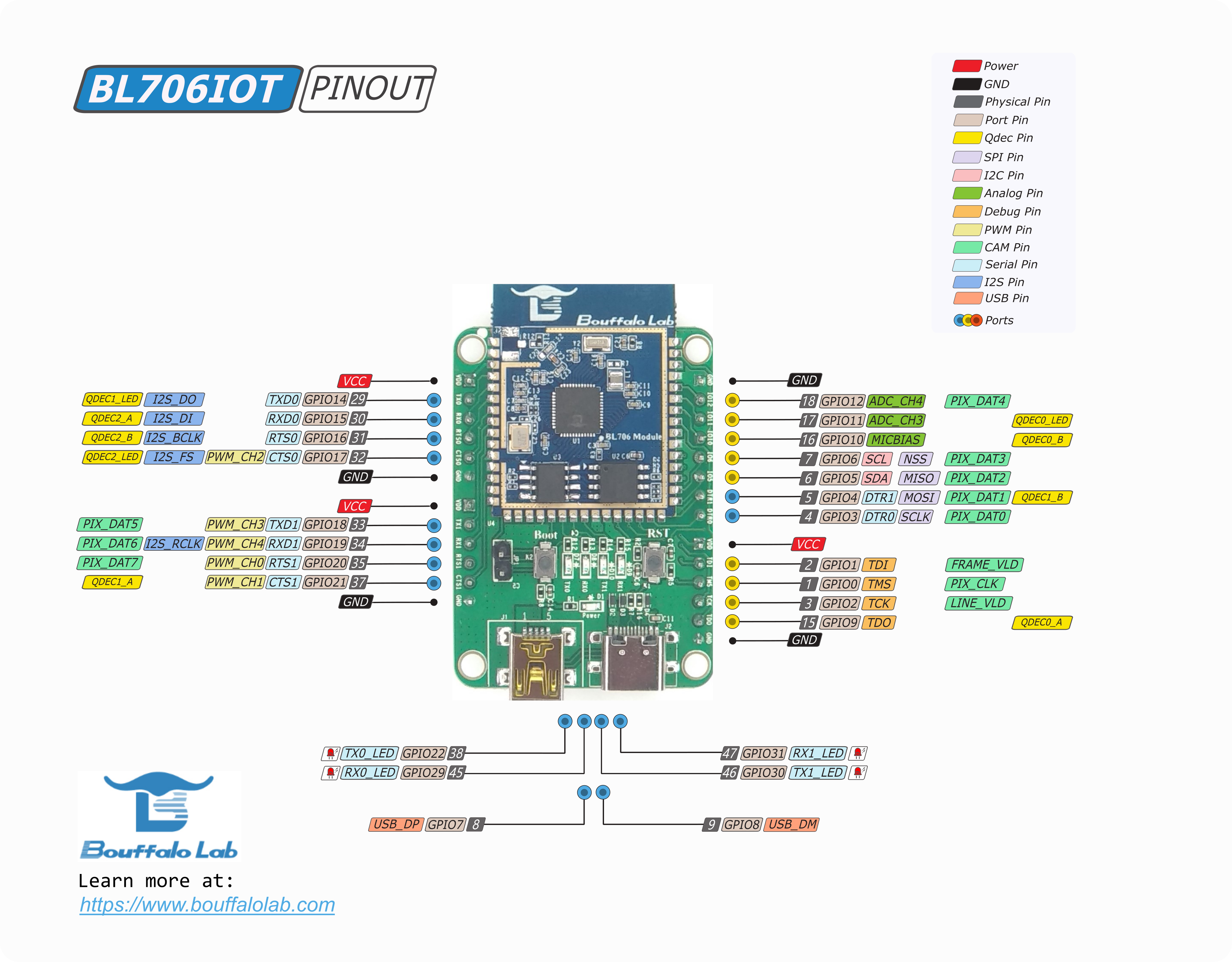

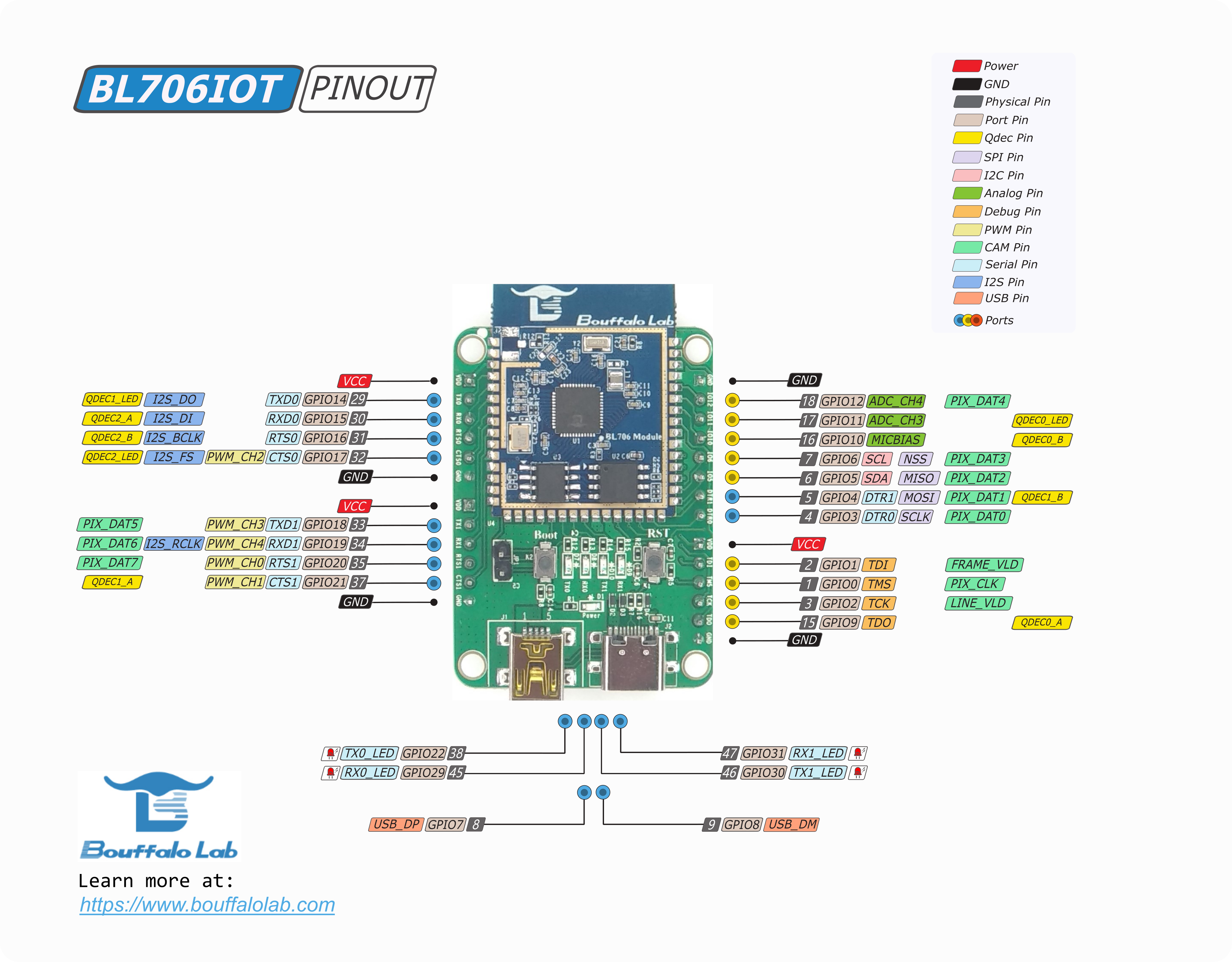

- BL706 IOT Development board

|

||||

[](https://imgtu.com/i/fnPcLT)

|

||||

|

||||

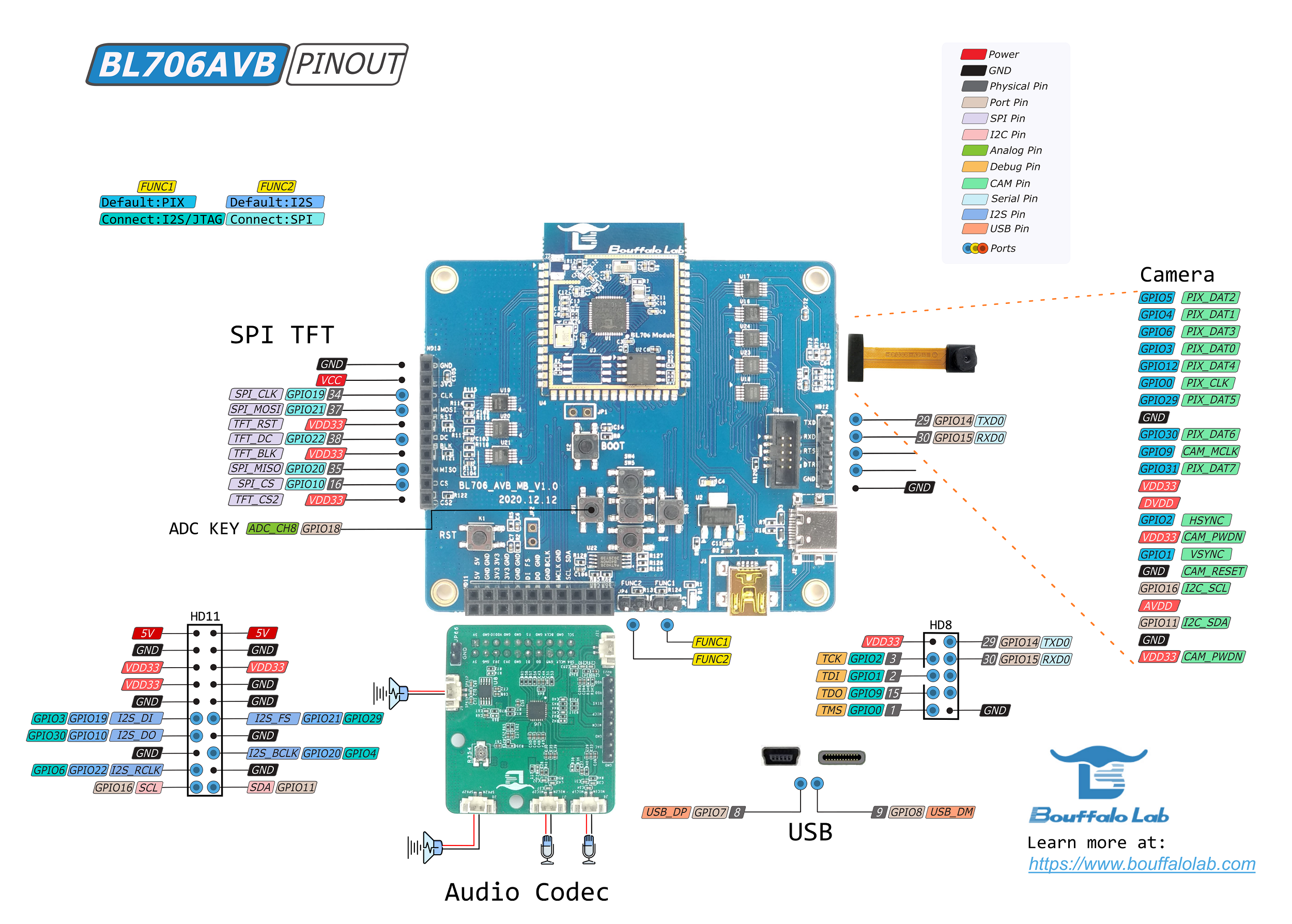

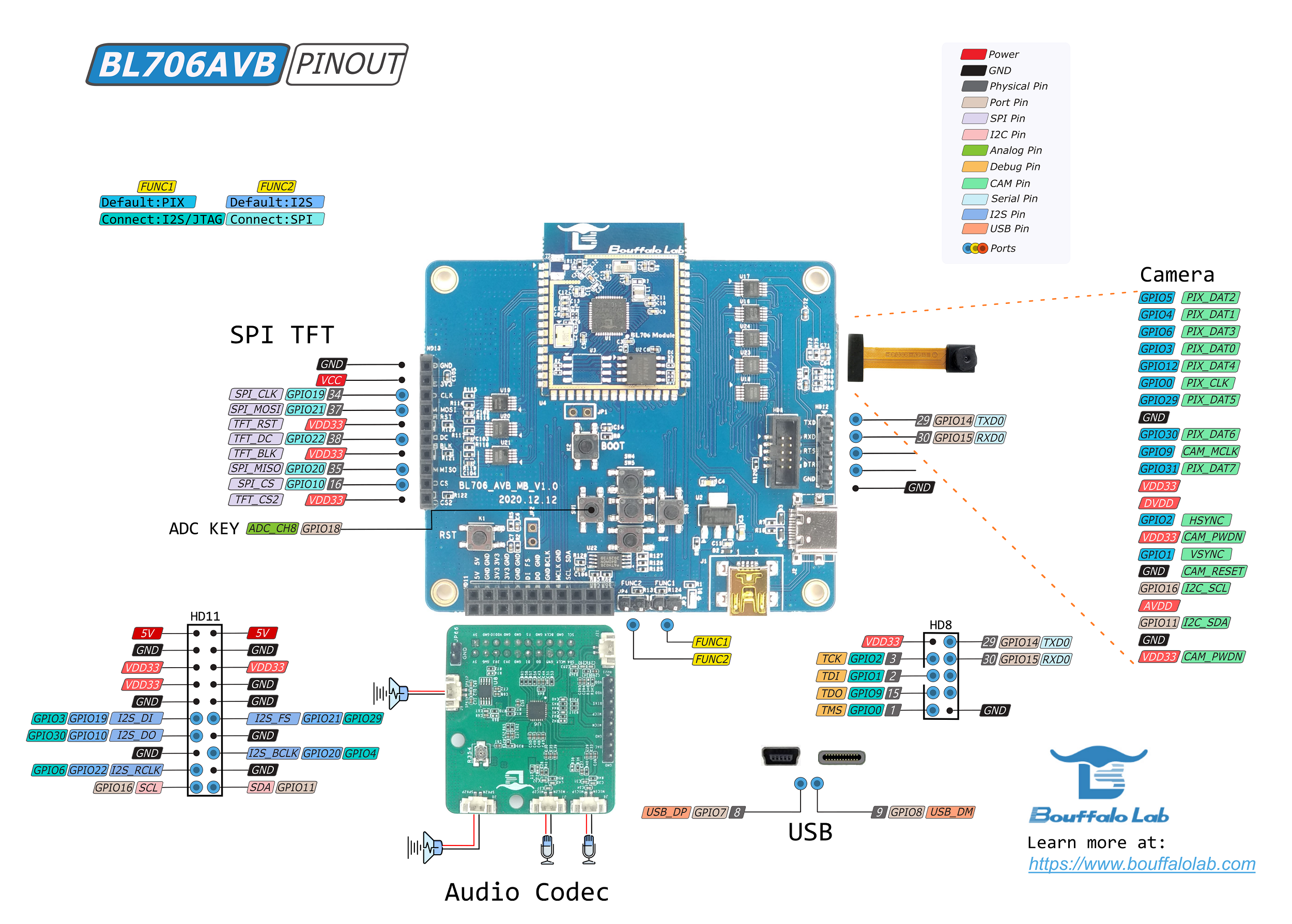

- BL706 AVB Development Board

|

||||

[](https://imgtu.com/i/IWPuVJ)

|

||||

|

||||

|

||||

There is currently no official purchase channel. If you want to get the above development board, you can apply for it in [Forum post](https://bbs.bouffalolab.com/d/88).

|

||||

|

||||

## Chip Manual

|

||||

|

||||

**Chip Reference Manual** and **Chip Data Manual** are listed on [document](https://dev.bouffalolab.com/document)

|

||||

|

||||

## Documentation Tutorial

|

||||

|

||||

To get more bl mcu sdk documentation tutorial, like api manual or peripheral demo and so on, please visit:

|

||||

|

||||

- [bl mcu sdk documentation tutorial](https://dev.bouffalolab.com/media/doc/sdk/bl_mcu_sdk_en/index.html)

|

||||

|

||||

## Video Tutorial

|

||||

|

||||

- [BL706 MCU Development Series Video Tutorial](https://www.bilibili.com/video/BV1xK4y1P7ur)

|

||||

|

||||

## Development Tools

|

||||

|

||||

### Command Line Development

|

||||

|

||||

For the tools needed for command line development, please refer to [linux development guide](https://dev.bouffalolab.com/media/doc/sdk/bl_mcu_sdk_en/get_started/Linux_quick_start_ubuntu.html)

|

||||

|

||||

- [cmake 3.19](https://cmake.org/files/v3.19/), cmake compilation tool, it is recommended to use cmake v3.15 or above

|

||||

- [riscv64-unknown-elf-gcc](https://gitee.com/bouffalolab/toolchain_gcc_sifive_linux), risc-v linux toolchain,download command:

|

||||

|

||||

```

|

||||

|

||||

git clone https://gitee.com/bouffalolab/toolchain_gcc_sifive_linux.git

|

||||

|

||||

```

|

||||

|

||||

### Eclipse Development

|

||||

|

||||

For the tools needed for Eclipse development, please refer to [Eclipse Development Guide](https://dev.bouffalolab.com/media/doc/sdk/bl_mcu_sdk_en/get_started/Windows_quick_start_eclipse.html)

|

||||

|

||||

- [Eclipse](https://dev.bouffalolab.com/media/upload/download/BouffaloLab_eclipse_x86_64_win.zip) eclipse development free installation package under Windows

|

||||

- [riscv64-unknown-elf-gcc](https://gitee.com/bouffalolab/toolchain_gcc_sifive_windows), risc-v windows toolchain,download command:

|

||||

|

||||

```

|

||||

|

||||

git clone https://gitee.com/bouffalolab/toolchain_gcc_sifive_windows.git

|

||||

|

||||

```

|

||||

|

||||

- [J-Link v10](https://www.segger.com/downloads/jlink), J-Link debugger, used to debug the chip online, it is recommended to use the hardware of J-Link V10 or above, and the software driver is recommended to use V6 .98 version

|

||||

|

||||

### CDK Development

|

||||

|

||||

For tools needed for CDK development, please refer to [CDK Development Guide](https://dev.bouffalolab.com/media/doc/sdk/bl_mcu_sdk_en/get_started/Windows_quick_start_cdk.html)

|

||||

|

||||

- [CDK](https://occ.t-head.cn/development/activities/cdk), Jianchi CDK integrated development environment of T-Head , it is recommended to use CDK v2.8.4 or above

|

||||

|

||||

### Flash Tool

|

||||

|

||||

In addition to using CK-link, J-link and command line programming, it also supports graphical programming tools.

|

||||

Graphical programming tools provided by Bouffalolab:

|

||||

|

||||

- [Bouffalo Lab Dev Cube](https://dev.bouffalolab.com/download)

|

||||

|

||||

### Board Config Wizard

|

||||

|

||||

We provide [BL Config Wizard](https://dev.bouffalolab.com/media/config/index.html) to generate `clock_config.h`、 `pinmux_config.h` and `peripheral_config.h` file online.

|

||||

|

||||

## How to make sdk as submodule

|

||||

|

||||

First add bl_mcu_sdk to your own project using the add submodule command, and then commit the gitmodules file to the remote repo.

|

||||

|

||||

|

||||

```

|

||||

|

||||

git submodule add https://gitee.com/bouffalolab/bl_mcu_sdk.git bl_mcu_sdk

|

||||

cd bl_mcu_sdk

|

||||

git pull --rebase

|

||||

cd ..

|

||||

git add .gitmodules

|

||||

git add bl_mcu_sdk

|

||||

git commit -m "xxx"

|

||||

git push

|

||||

|

||||

```

|

||||

|

||||

The final catalog presents the following results:

|

||||

|

||||

```

|

||||

.

|

||||

├── hardware

|

||||

├── xxxx

|

||||

├── xxxx

|

||||

├── xxxx

|

||||

├── bl_mcu_sdk

|

||||

├── user_code

|

||||

│ └── gpio

|

||||

│ ├── gpio_blink

|

||||

│ ├── gpio_dht11

|

||||

│ └── gpio_int

|

||||

|

||||

```

|

||||

|

||||

### Command Line compile

|

||||

|

||||

```

|

||||

cd bl_mcu_sdk

|

||||

make APP=xxx APP_DIR=../user_code

|

||||

```

|

||||

|

||||

## Forum

|

||||

|

||||

Bouffalolab Developer Forum: [https://bbs.bouffalolab.com/](https://bbs.bouffalolab.com/)

|

||||

|

||||

# License

|

||||

|

||||

**bl mcu sdk** is completely open source and follows the Apache License 2.0 open source license agreement. It can be used in commercial products for free and does not require public private code.

|

||||

|

||||

```

|

||||

/*

|

||||

* Copyright (c) 2021 Bouffalolab team

|

||||

*

|

||||

* SPDX-License-Identifier: Apache-2.0

|

||||

*/

|

||||

```

|

||||

245

source/Core/BSP/Magic/bl_mcu_sdk/README_zh.md

Normal file

245

source/Core/BSP/Magic/bl_mcu_sdk/README_zh.md

Normal file

@@ -0,0 +1,245 @@

|

||||

[](LICENSE)

|

||||

[]()

|

||||

|

||||

[English Version](README.md)

|

||||

|

||||

# 简介

|

||||

|

||||

**bl mcu sdk** 是博流智能科技团队专为 BL602/BL604,BL702/BL704/BL706 以及未来其他系列芯片提供的 MCU 软件开发包。

|

||||

|

||||

## 代码框架

|

||||

|

||||

```

|

||||

|

||||

bl_mcu_sdk

|

||||

├── bsp

|

||||

│ ├── board

|

||||

│ │ ├── bl602

|

||||

│ │ └── bl702

|

||||

│ └── bsp_common

|

||||

├── build

|

||||

├── common

|

||||

│ ├── bl_math

|

||||

│ ├── device

|

||||

│ ├── list

|

||||

│ ├── memheap

|

||||

│ ├── misc

|

||||

│ ├── partition

|

||||

│ ├── pid

|

||||

│ ├── ring_buffer

|

||||

│ ├── soft_crc

|

||||

│ └── timestamp

|

||||

├── components

|

||||

│ ├── ble

|

||||

│ ├── fatfs

|

||||

│ ├── freertos

|

||||

│ ├── lvgl

|

||||

│ ├── lwip

|

||||

│ ├── mbedtls

|

||||

│ ├── nmsis

|

||||

│ ├── romfs

|

||||

│ ├── rt-thread

|

||||

│ ├── shell

|

||||

│ ├── tflite

|

||||

│ ├── tiny_jpeg

|

||||

│ ├── usb_stack

|

||||

│ └── xz

|

||||

├── docs

|

||||

│ ├── chipSpecification

|

||||

│ ├── development_guide

|

||||

│ └── development_guide_en

|

||||

├── drivers

|

||||

│ ├── bl602_driver

|

||||

│ └── bl702_driver

|

||||

├── examples

|

||||

│ ├── acomp

|

||||

│ ├── adc

|

||||

│ ├── audio_cube

|

||||

│ ├── ble

|

||||

│ ├── boot2_iap

|

||||

│ ├── camera

|

||||

│ ├── coremark

|

||||

│ ├── cxx

|

||||

│ ├── dac

|

||||

│ ├── dma

|

||||

│ ├── dsp

|

||||

│ ├── emac

|

||||

│ ├── flash

|

||||

│ ├── freertos

|

||||

│ ├── gpio

|

||||

│ ├── hellowd

|

||||

│ ├── i2c

|

||||

│ ├── i2s

|

||||

│ ├── keyscan

|

||||

│ ├── lvgl

|

||||

│ ├── mbedtls

|

||||

│ ├── memheap

|

||||

│ ├── nn

|

||||

│ ├── pka

|

||||

│ ├── pm

|

||||

│ ├── psram

|

||||

│ ├── pwm

|

||||

│ ├── qdec

|

||||

│ ├── rt-thread

|

||||

│ ├── rtc

|

||||

│ ├── shell

|

||||

│ ├── spi

|

||||

│ ├── systick

|

||||

│ ├── tensorflow

|

||||

│ ├── timer

|

||||

│ ├── uart

|

||||

│ └── usb

|

||||

├── out

|